|

It is shown that the difference between the p- and n-channel. Note that due to multiple scattering the resolution is limited. nMOS transistor threshold voltages (VT) in CMOS digital circuits power dissipation is investigated. Also listed is the general form of the associated MOSFET model statement. For the irradiated chip in (c) there are only slightly less efficient regions in the regions between pixels. 5.1: Spice element description for the NMOS and PMOS MOSFETs. Applying SiGe in source and drain areas can realize compressive local strain, which is suited to boosting the performance of pMOS devices.

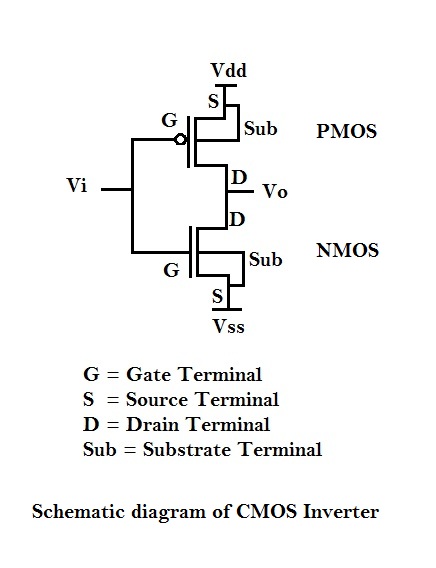

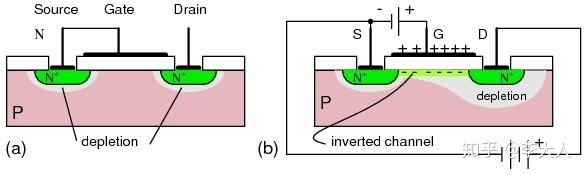

Download : Download full-size image Download : Download full-size image Figure 3. In un-irradiated chips (b), the hit detection efficiency is homogeneous throughout the pixels. Any technique that can boost the performance of pMOS to the level of nMOS is therefore considered advantageous. The n-wells act as as charge collection nodes and the p-wells separate the collection node from each other. In (a), n-well, p-well and active area are shown in red, blue, and green respectively. In-pixel efficiency: (a) Layout of four pixels near corners and measured hit detection efficiency maps for (b) un-irradiated and (c) neutron irradiated LF-Monopix1. The masked regions and edges of measured area were excluded from the efficiency calculation. Five and one pixel were masked in the un-irradiated and irradiated chip, respectively. The results from MOS capacitors comprising interface state density. Non-efficient areas correspond to masked pixels. The observed instability of PMOS devices is more significant than in equivalent NMOS devices. The gate voltages applied to these two transistors are also. The hit detection efficiencies are (99.7$\pm$0.1)\% and (98.9$\pm$0.1)\% for un-irradiated and irradiated chip, respectively. The CMOS transmission gate consists of one nMOS and one pMOS transistor, connected in parallel. : : Schematics of three preamplifier designs using \subref$) LF-Monopix1. In reality, the dimensions of the well structures are negligible in depth compared to the sensitive volume (p-substrate).Ĭircuit diagram of the analog front-end circuit. The drawing is not to scale and only illustrates the relative implantation depths of different wells. The p-wells (PW) on both sides of DNW are p-stop implants to isolate two neighboring pixels. A deep p-well (PSUB) is used to shield the n-well (NW) hosting the PMOS transistor from the charge collection node. The charges created in the p-substrate are collected by a n-type collection electrode formed by a very deep n-well implant (DNW). There are two types of MOSFET transistors: PMOS and NMOS. Red color represents n-type material and blue color represents p-type material. The drain terminals are connected together as a common output.Schematic cross-section of a pixel cell implemented in the LFoundry 150~nm CMOS technology. The gate of both the devices are connected together and a common input is given to both the MOSFET device. The source terminal of the N-channel device is connected to the ground. The source terminal of the P-channel device is connected to source voltage +V DD. In CMOS inverter, both the n-channel and p-channel devices are connected in series. Now let us look at the CMOS logic family.

CMOS also has more fan-out and better noise margin. However, the speed of operation is high and power dissipation is less in CMOS. When a circuit contains both NMOS and PMOS transistors we say it is implemented in CMOS. CMOS has greater complexity than PMOS and NMOS. Thus negative voltage(LOW voltage) is enough to turn ON the PMOS devices.ĬMOS(Complementary MOS) logic family uses both N-channel and P-channel MOSFET devices. The operation of PMOS is similar to the NMOS circuits, except that the mode of conduction is different.įor a P-channel MOSFET, a negative voltage is to be given at the gate terminal to create a channel. Similarly, if both the inputs are HIGH, it will turn ON both the MOSFETs, which will make the output to be LOW.Īs discussed above, the digital logic family can be built with P-channel MOSFETs and those circuits are known as PMOS logic circuits. If any of the input, either A or B is given HIGH input, the corresponding MOSFET with HIGH input will turn ON making the output to be LOW. If Low input is given at both the inputs, it will turn OFF both the MOSFETs Q 2 and Q 3, thereby making the output to be HIGH.

0 Comments

Leave a Reply. |

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed